Goal

Our research goal is to explore the optimal analog circuit and system architecture with diminishing power/area consumption and design effort in the future nano-scale technologies. In many cases, we aim at reshaping the analog and digital boundary of the circuit/system architecture, and leveraging what technology scaling offers to address the future analog design challenges.

At the circuit level, we are interested in pushing the boundary of various critical analog mixed-signal, RF components, such as data converters (ADC, DAC), power amplifier (PA), phase locked loop (PLL) frequency synthesizer, etc. At the system level, we are also interested in wireless/wireline communication systems and emerging applications, such as bio-related, sensing systems, computing platform (machine learning/artificial intelligence/neural network).

To address the increasing design complexity in scaled technology, we are exploring machine learning based CAD tools for future analog circuit design automation.

Our current research activities generally span over the following areas: (1) data converter, (2) wireless, (3) wireline, (4) computing, and (5) design methodology.

Key Group Contributions

- Asynchronous SAR ADC (since 2006)

- Embedded TDC scheme for DPLL (since 2010)

- Nonuniform sampling (NUS) ADCs and NU DSP (since 2012)

- Direct spur/pulling cancellation for DPLL (since 2014)

- Dual-rate hybrid DAC (since 2014)

- Dual reference shifting SAR ADC (since 2016)

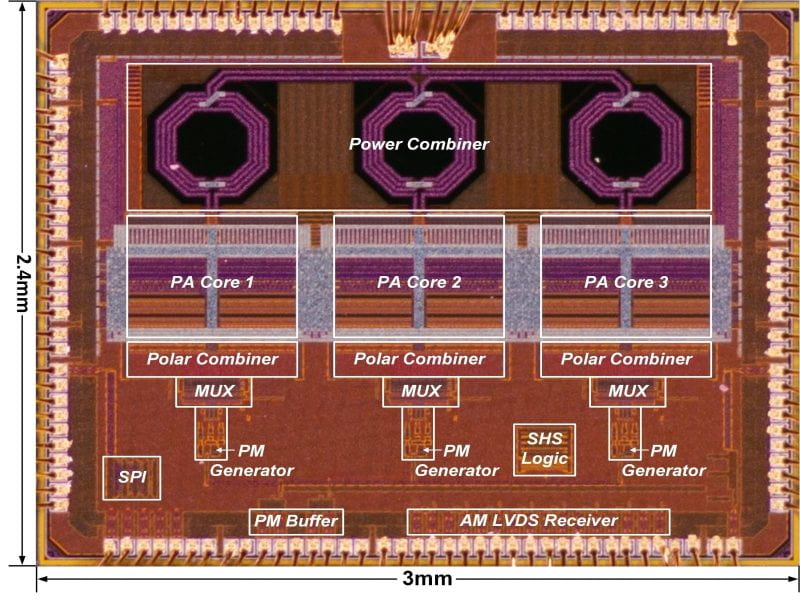

- Sub-harmonic switching (SHS) PA (since 2018)

- Time-Approximation Filter (TAF) (since 2019)

- Two-Point DTC Calibration scheme for MDLL (since 2021)

- Delay-tracking pipelined SAR TDC (since 2022)

Comic Book of Our Research

The Greatest Thing You’ll Never See